Panel Level Packaging

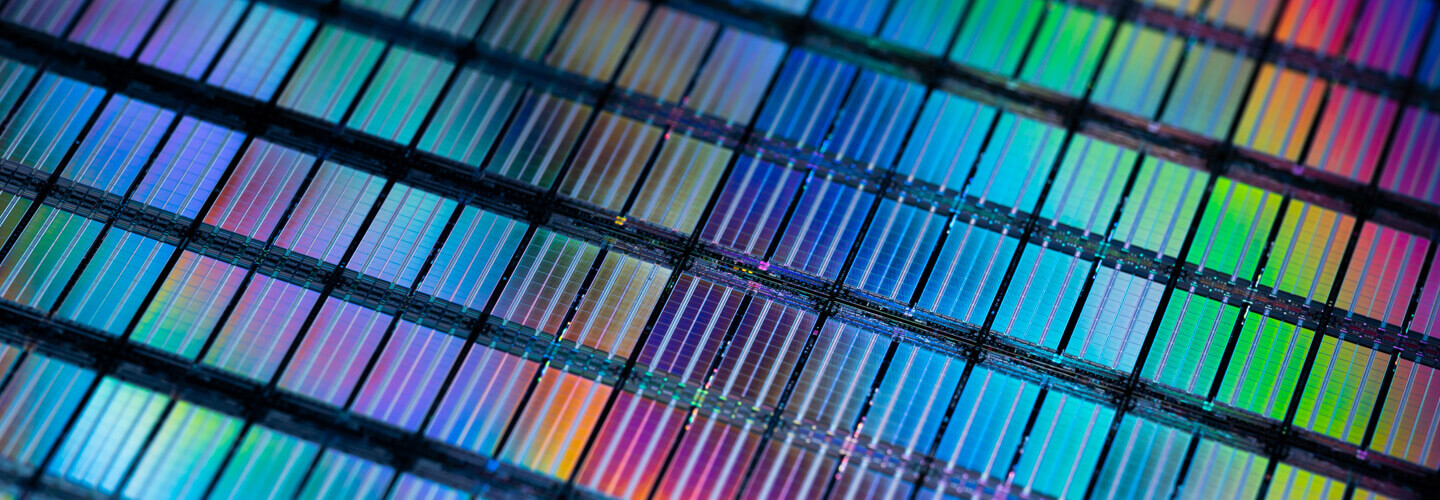

Fan-Out Panel Level Packaging (FOPLP) Overview

Wafer-level packaging for 2.5D and 3D packaging technologies is transitioning from fan-out wafer-level packaging (FOWLP) to fan-out panel-level packaging (FOPLP). Moving to FOPLP will help reduce processing bottlenecks and improve cost and packaging yield. ACM Research has applied its expertise in FOWLP technology to develop the first-of-its-kind panel-level processing tool that will enable customers to achieve their panel-level processing goals.

Capable of Multiple Panel Processes

Leveraging the company’s expertise in the packaging cleaning and plating process, ACM Research’s suite of panel-level process tools offers a multitude of capabilities to meet customers’ advanced panel-level processing needs and build the challenging structures for advanced packaging requirements.

- The Ultra C vac-p Flux provides superior vacuum-based cleaning technology for the removal of contaminants in hard-to-reach spaces, especially in the bumping process.

- The Ultra ECP ap-p can be used for plating steps in a variety of processes including pillar, bump, and RDL. The panel plating equipment can also be utilized for fan-out and through-glass via (TGV) processes.

- The Ultra ECP ap-p can support up to 16 plating chambers for copper, nickel, tin-silver, gold, and other plating materials.

- The Ultra ECP ap-p can handle organic and glass substrates sized 510 x 515 mm2 and 600 x 600 mm2 while effectively managing cover warpages up to 7 mm.

- The Ultra ECP ap-p provides cost-effective, high-yield FOPLP processing technology.

- The Ultra C bev-p double-sided bevel etching tool is capable of bevel etch and copper removal for panel-level packaging.

As a leader in FOWLP process equipment, ACM Research can accommodate special process requests and deliver custom-made, differentiated panel-level processing equipment at a competitive price.

Panel Level Packaging—Ultra ECP ap-p

Learn More

Panel Level Packaging—Ultra C vac-p Flux Cleaning Tool

Learn More

Panel Level Packaging—Ultra C bev-p tool

Learn MorePanel Level Packaging FAQ

Contact Us

We look forward to providing customized solutions for your wet wafer processing, ECP, Furnace, Track, PECVD, and SFP applications.