By Sally-Ann Henry and Jim Straus, ACM Research

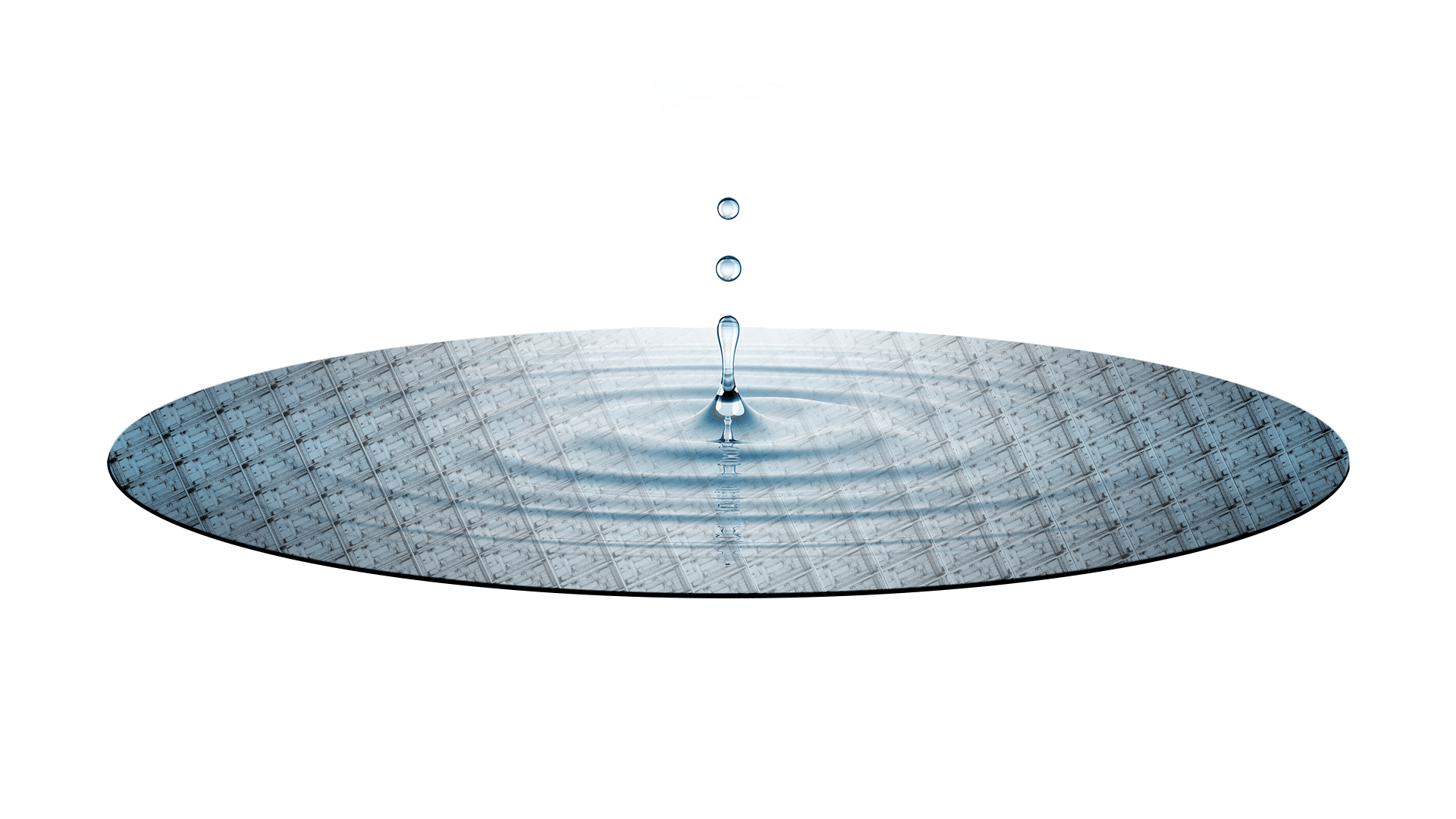

While it might not sound as sexy as extreme ultraviolet (EUV) lithography, wet wafer cleaning technology might be even more crucial than EUV for ensuring successful leading-edge node, advanced semiconductor device manufacturing. This is because both device reliability and final product yields are directly linked to the cleanliness of a wafer as it passes through the hundreds of patterning, etching, deposition and interconnect process steps.

Just a single particle on a wafer is enough to cause a killer defect or excursion that will ultimately lead to device failure. Today’s most advanced node devices are used in critical applications like smart automotive, health care and industrial applications. Consequently, device reliability is more important than ever. This means more stringent sorting and binning of devices, which impacts yield.

Unfortunately, many conventional approaches to wafer cleaning are not only insufficient for advanced node technology, they can also cause damage to delicate structure like finFETs and through silicon vias. Therefore, choosing the right wet wafer cleaning technology should not be left as an afterthought, but considered carefully as part of a robust manufacturing process flow.

With that in mind, let’s look at how wet wafer cleaning technology has evolved from an art to a science, and how wet wafer cleaning technology is developed specifically for the needs of advanced technology nodes.

How Many Cleaning Steps are There?

45nm node technology calls for approximately 150-200 separate cleaning process steps. 10nm node processing used 3X that number, ~800 cleaning process steps, including:

- Photoresist strip

- Post-etch strip

- Implant strip

- General wafer cleaning

- Backside cleaning for multiple patterning and EUV

Shrinking technology nodes required double-, triple- and even quadruple-patterning lithography processes. This added hundreds of additional steps to the overall process flow, including additional cleaning steps. While the introduction of EUV reduces the number of process steps, even finer features are now possible, increasing the need for advanced wafer surface preparation that won’t damage delicate structures.

Wet Wafer Cleaning Technologies Evolved

For decades, different wet wafer cleaning technology approaches have been used to remove unwanted particles, contaminants and metallics from the wafer’s surface, preparing it for the next step in the process. In their book, Handbook of Silicon Wafer Cleaning Technology, co-editors Karen Reinhardt and Werner Kern state that “in the past, wafer cleaning and surface preparation were considered more of an art than a science.” But that has changed.

Wet Bench Approach

In the early days, when wafers measured 150mm in diameter and technology nodes were above 45nm, wet bench batch processing was sufficient. The motivation for wet bench wet wafer cleaning was throughput and convenience. As a batch process, 25-50 wafers could be moved through the cleaning steps efficiently.

This simple process involved immersing a wafer batch into the cleaning chemistry in an open wet bench to loosen and remove particles, metallics and other contaminants. Unfortunately, wet bench cleaning was difficult to control and was not sufficient for removing submicron particles from finer trenches and vias. In fact, the immersion process caused chemistry to run down the wafer and leave particles behind. Additionally, as an open process, there are health and safety implications. As a result, today a wet bench approach is only used for silicon nitride stripping.As wafers got larger, and vias, trenches and interconnect technologies got smaller, cleaning and surface preparation became more complex. The focus shifted from merely cleaning to surface preparation. The goal is to make sure the wafer surface is particle-free without being damaged, and also optimized for the next step, such as film deposition. This called for more scientific approaches that allowed for cleaning to be fine-tuned to suit the situation.

Batch Spray Approach

Batch spray was adopted next in the evolution of wet wafer cleaning technologies. Spraying the wafers increased the velocity of the chemistry, improving the ability to dislodge particles from wafer features. Because wafer batches are enclosed in the spray chamber, it’s a safer system. However, by virtue of being a batch process, it is still subject to related challenges. One of these is the mirror effect created by sprayed wafers sticking together, so that chemistry can’t reach the wafers’ surface to clean them.

Single Wet Wafer Cleaning

Single wet wafer cleaning technology using a spray approach is now the preferred approach for performing the many cleaning steps for technology nodes from 45nm down, manufactured on 200 and 300mm wafers. The spray is easier to control, and while throughput can be an issue, it is offset by the benefit of yield improvements due to cleaner wafers with fewer defects.

The challenge with conventional spray approaches is that the aerosol can’t always achieve the proper angle or depth to thoroughly clean vertical features and deep holes. Additionally, the force of the spray may cause damage to delicate features.

Megasonic Spray Cleaning

At ACM Research, we’ve taken single wet wafer cleaning to the next level with our state-of-the-art Space Alternated Phase Shift (SAPS™) megasonic cleaning process. There is a fine line between cleaning a wafer sufficiently and causing damage. SAPS makes it possible to control the distance between the megasonic cell and the wafer. Additionally, our SAPS process uses a Lamb wave that permeates the silicon and thins the boundary layer of the chemistries to fine-tune backside cleaning. Lastly, our proprietary Timely Energized Bubble Oscillation (TEBO™) megasonic technology cleans “sensitive” structures at 28nm and below by stabilizing the cavitation to prevent damage caused by bubble implosion during the cleaning process. The result is a uniform, damage-free clean, from the flattest surface and deepest vias to the most delicate structures.

Conclusion

State-of-the art wet wafer cleaning technologies have evolved from wet bench, to batch spray, to single-wafer spray approaches. This transition was driven by the need for improved reliability and yield of advanced technology node semiconductor devices. ACM’s SAPS megasonic cleaning uses results in a uniform clean with reduced damage to wafer structures. To learn more about the science of TEBO megasonic cleaning, download our white paper.